test tile on substrate for electronic package|High : suppliers A typical test flow is shown in Figure 13-1 which consists of a substrate test to guarantee a known-good substrate, assembly of known good die after bum-in to the substrate, and a final . WEB21 de jun. de 2020 · 半导体集成电路系列 (二):MOSFET. 当今的集成电路,实时性和低功耗方面,在复杂的三维飞行控制上仍无法与蜻蜓的大脑竞争,这是60年的集成电路历史与40亿年的生命演化无法比拟的,不幸的是,目前我们仍不知道如何在集成电路中实现如此惊人的生命算法。. 1 .

{plog:ftitle_list}

Resultado da Rebolo (pt-BR) ou Mó (pt-PT) é a mesa de profissão do armeiro, usado para reparar itens e ferramentas, ou remover encantamentos. O rebolo deve ser minerado com uma picareta ou ele não largará nada. A pedra de amolar é gerada na casa do armeiro nas vilas. A receita necessita de Gravetos que .

These best practices are defined as: Achieving substrate supplier’s fabrication requirements. Shifting-left “big-rock” power delivery analysis. Adopting efficient integration methodologies for HBM memory. Leveraging concurrent team design. Utilizing physical design IP reuse. .To achieve the lowest scrap cost, methods of testing the interposer die before it is attached to a substrate should be explored. An easier approach, but at a slight higher cost, would be .The substrate of the package is the semiconductor die with or without a redistribution layer that may have a square or rectangular shape with metallic balls applied onto the circuit side of the die.electronic packages. Electronic packaging provides the in-terconnection from the IC to the printed circuit board (PCB). Another function is to provide the desired mechanical and .

A typical test flow is shown in Figure 13-1 which consists of a substrate test to guarantee a known-good substrate, assembly of known good die after bum-in to the substrate, and a final . Design daisy-chain test vehicles efficiently; Use datapath planning and routing; Achieving substrate supplier fabrication requirements. Package fabricators have strict metal .

In this paper, a risk assessment testing methodology built in the fundamentals of packaging physics of failure is discussed in terms of reliability tests and package assembly process .Substrate players are developing smaller L/S IC substrates by stacking a thin-film RDL substrate on the build-up IC substrate. This enables advanced substrate technologies with . Dielectric tests were performed on the double-layer ceramic packaging substrates before and after thermal tests. A direct current (DC) voltage was applied across the bottom .To choose the perfect IC package or IC substrate, you should understand and examine the various technical factors of integrated circuit design. For example, you know the proper material composition and substrate for your integrated .

We will delve into the various applications where these substrates play a crucial role, including power electronics, LED technology, and electronic packaging. Whether you are an engineer, designer, or simply someone interested in the .

The Seven Pillars Of IC Package Physical Design

Abstract. A double-layer ceramic electronic packaging technology that survives the Venusian surface temperature of 465°C was developed using a ceramic interlayer dielectric with gold conductors. A 60-μm ceramic interlayer dielectric served as the insulator between the top and bottom gold conductors on high-purity ceramic substrates. Test devices with AuPtPd . It is the most commonly used substance in ceramics as it has many applications in electronics, including substrates and packages. When the application does not require the maximum level of thermal performance, this is the go-to material in use. It is one of the most researched and thoroughly characterized advanced ceramic materials now available.This unusual combination of properties makes AlN a critical advanced material for many future applications in electronic packages. Due to the high thermal conductivity, AlN efficiently releases the heat from high heat generating IC chips. . Square Substrates: Thickness: 0.385mm, 0.5mm, 0.635mm, 1mm Length x Width (mm): 50.8 x 50.8, 76.2 x 76. . The package substrate provides electrical connection between the chip and different circuits of the conventional PCB, and provides protection, support, heat dissipation channels for the chip, and achieves the effect of meeting the standard installation size. With the development of technology, semiconductor package substrates in the form of BGA, CSP and .

The external surfaces of the electronic package enclosure should have an optimum surface finish, better hardness, scratch resistance and hydrophobic surface. . Test. (2016) M.H. Rahimi et al. . there is an urge for high scratch-resistant coating on enclosure surface [4]. Parallelly, nanoporous AAO-np on Al5052 substrate potentially improves .

3 Outline 5 • Introduction • Moisture absorption, desorption, and diffusion • Vapor pressure model • CtdICase study I – und fill l ti f FC BGA kderfill selection for FC BGA packages • Case study II – delamination/cracking in stacked-die chip scale packages • Accelerated moisture sensitivity test • Effect of moisture on material properties • Hygroscopic swelling

The package substrate of claim 1, further comprising a first dielectric layer disposed between the magnetic layer and the first conductive trace. 3. The package substrate of claim 2, wherein the first dielectric layer is disposed in the first recess of the magnetic layer, and partially surrounds the first conductive trace. 4.

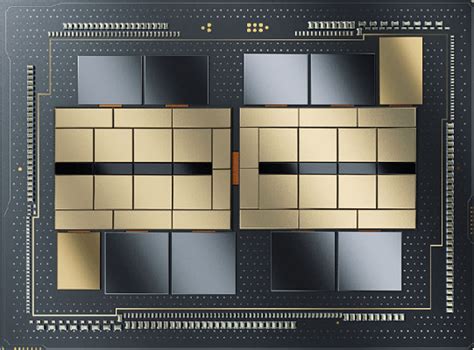

Status of Advanced Packaging and IC Substrate

Semiconductor Packaging Assembly Technology

Recent Advances and Trends in Advanced Packaging

The design of the substrate affects the accessibility of test points and the ease of interfacing with testing equipment. Proper integration of the package substrate with testing systems ensures accurate and efficient testing, facilitating the identification of potential issues and ensuring that only high-quality ICs reach the market . BGA Package Substrates: An Overview Definition and Role of the Substrate in BGA Packages. The substrate in BGA packages serves as the foundation upon which the integrated circuit (IC) is mounted. It acts as a medium for connecting the IC to the rest of the system, typically via wire bonding or flip chip technology.

A typical surface mount assembly involves mounting electronic packages onto the printed circuit board (PCB). . require you to apply the process of underfill for the bonding between the die and the substrate. As part of the design and mechanical validation, OEMs look to perform tests that measure the bond strength of the adhesives in a package .

Semiconductor packaging is a crucial aspect of electronics manufacturing that involves enclosing semiconductor chips in protective and functional packages to ensure their reliability, performance and integration into electronic devices. These packages serve as a bridge between the tiny, sensitive semiconductor chips and the broader electronic systems, providing electrical .

electronic packages. Electronic packaging provides the in-terconnection from the IC to the printed circuit board (PCB). Another function is to provide the desired mechanical and environmental protection to ensure reliability and perfor-mance. Three fundamental assembly flow processes (Table 1) are covered in this chapter: 1) plastic leadframe-based Miniaturization and Form Factor Optimization: Package substrates with compact designs, such as 4-layer package substrate, enable Samsung to develop smaller and more compact semiconductor packages. .tor substrates used at the chip/package level and ceramic-based power electronic substrates used at the package and/or circuit board level. Some thin- or thick-film processes may also leverage ceramic materials as the base layer for the film-based components. This technical brief is aimed at educating designers and system integrators

Ask the Chatbot a Question Ask the Chatbot a Question electronic substrate and package ceramics, advanced industrial materials that, owing to their insulating qualities, are useful in the production of electronic components.. Modern electronics are based on the integrated circuit, an assembly of millions of interconnected components such as transistors and resistors that are .Substrate players are developing smaller L/S IC substrates by stacking a thin-film RDL substrate on the build-up IC substrate. This enables advanced substrate technologies with integrated interposer or RDL technology for 2.5D/3D advanced packaging. • A heterogeneous integration solution for multiple dies on the substrate.package – where a chiplet is defined as an ASIC die specifically designed and optimized for operation within a package in conjunction with other chiplets. Historically IC package design has been a relatively simple task which allowed the die bumps to be fanned out on a package substrate with a floorplan geometry suitable for connecting to a PCB.

In addition also a stamped prepreg is placed on the substrate. The lid tile is aligned and in a tile level sinter process the interconnects are obtained and the prepreg is cured and seals the package.

What is a PCB Substrate? Definition and Function: A PCB substrate, also known as the base material or core material, is the foundational layer upon which electronic components are mounted and interconnected to form a printed circuit board (PCB). It serves as the physical platform for building electronic circuits and plays a crucial role in their functionality and .PFAS-Containing Materials Used in Semiconductor Manufacturing Assembly Test Packaging and Substrate Processes . . in one assembly material could require testing across multiple silicon die or second-level interconnect vendors or the electronic customer incorporating the package into their final product. .

is the idaho drivers license test hard

BGA Substrates: These substrates are suitable for IC packages with a large number of pins (>300). They are primarily attributed to their excellent electrical performance and heat dissipation capabilities. Chip-Scale Package (CSP) IC Substrates: These substrates are characterized by their miniaturized and thin form factor. Hence, they are .

The design of fireball heater, a novel test chip structure used for evaluating the effectiveness of heat spreading of advanced thermal solutions, is also explained., – Describes the design considerations and processes of the package substrate and printed‐circuit board with special emphasis on the physical routing of the thermal test chip . Fortunately, ceramic substrate materials can meet the electrical and mechanical requirements of EV and HEV power modules as well as many other power electronic applications. The ceramic substrates include copper layers for fabrication of circuit patterns, heat sinks, and other electronic structures.The structural integrity of electronic packages is significantly influenced by the presence of moisture in the packages. Many failures in microelectronic packages can be traced back to moisture [1-3]. In general, there are three types of failure mechanisms when an electronic package is exposed to humidity conditions.Structure of a direct bonded copper substrate (top) and an insulated metal substrate (bottom). DBC substrates are commonly used in power modules, because of their very good thermal conductivity. [1] They are composed of a ceramic material tile with a sheet of copper bonded to one or both sides by a high-temperature oxidation process (the copper and substrate are .

is the ie admission test hard

web13 de fev. de 2020 · 开发人员: (Adaltech); 价格: (免费); 列表: (0); 积分: (0); 版本: (1.8.6); RSS: (+); 可选. 添加到列表. 详细了解 9ingressos - POS-APP 应用.

test tile on substrate for electronic package|High